Jee and Rich are in Phoenix this week for IPDPS’14, where Jee will present his latest updates to his “energy roofline” model [Tue May 20, Session 11] :

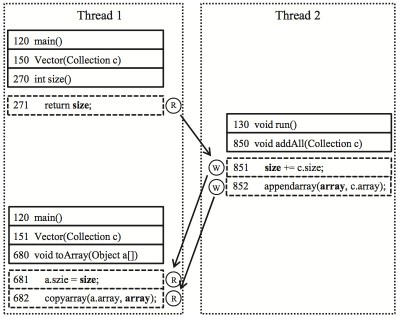

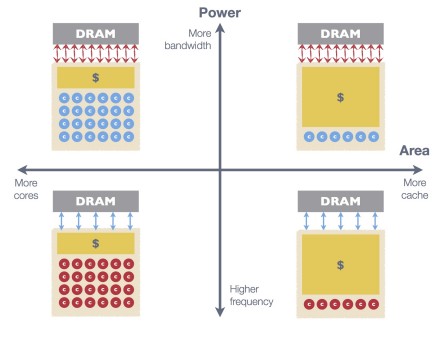

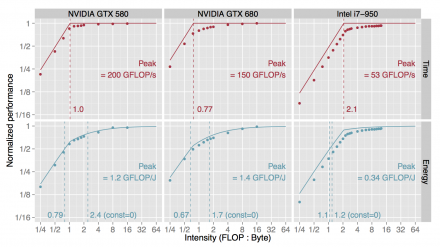

- Jee Choi, Marat Dukhan, Xing Liu, and Richard Vuduc. Algorithmic time, energy, and power on candidate HPC compute building blocks. In Proc. IEEE Int’l. Parallel and Distributed Processing Symp. (IPDPS), Phoenix, AZ, USA, May 2014. [PDF preprint | PDF slides]

Rich also has the pleasure of serving in a panel discussion at the High-Performance, Power-Aware Computing workshop. His position is that power-aware scheduling is really an optimal control problem. For his 1-slide summary, see: [link]

Outside our group, Georgia Tech has a very strong representation this year. Looking at the program, we count 9 papers, including two of the four “Best Papers.” Go, Buzz!

Jee chowing down on a pre-conference pulpo at Mariscos Sinaloa.